Memory complier 虚拟机使用

Memory complier 虚拟机使用

虚拟机密码 2022

先看一遍PDF,然后PDF中个别有误,在后面给出正确步骤。

[t28_sram.pdf]

__1.进入路径: /home/ICer/IC_prj/T28_SRAM/T28 __

在 /home/ICer/IC_prj/T28_SRAM/T28/license目录下新建终端,终端中执行命令,执行结束不要关闭!后面要用。

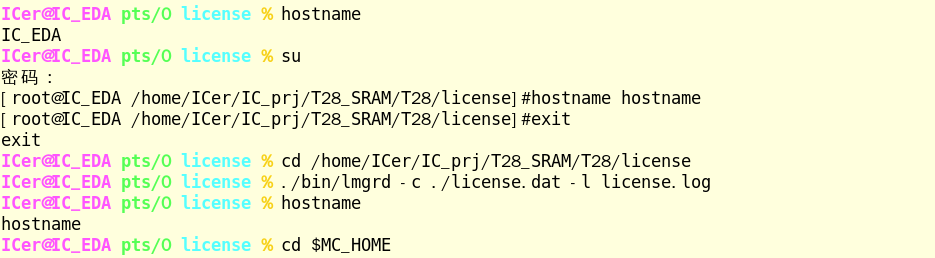

输入hostname,如果输出不是hostname,就修改为hostname。要进入管理员模式修改。更改指令:

1 | su |

/home/ICer/IC_prj/T28_SRAM/T28/license/license.dat前两行,不一致就修改

1 | SERVER hostname 908d6efda35b 26000 |

1 | setenv PATH_T28 /home/ICer/IC_prj/T28_SRAM/T28 |

1 | # 执行命令 |

1 | # 测试命令 |

以上都正常,说明环境没问题,接下来的操作就生成你需要的sram。

打开的这个终端不要关闭,接下来的命令都在这个终端中输入。

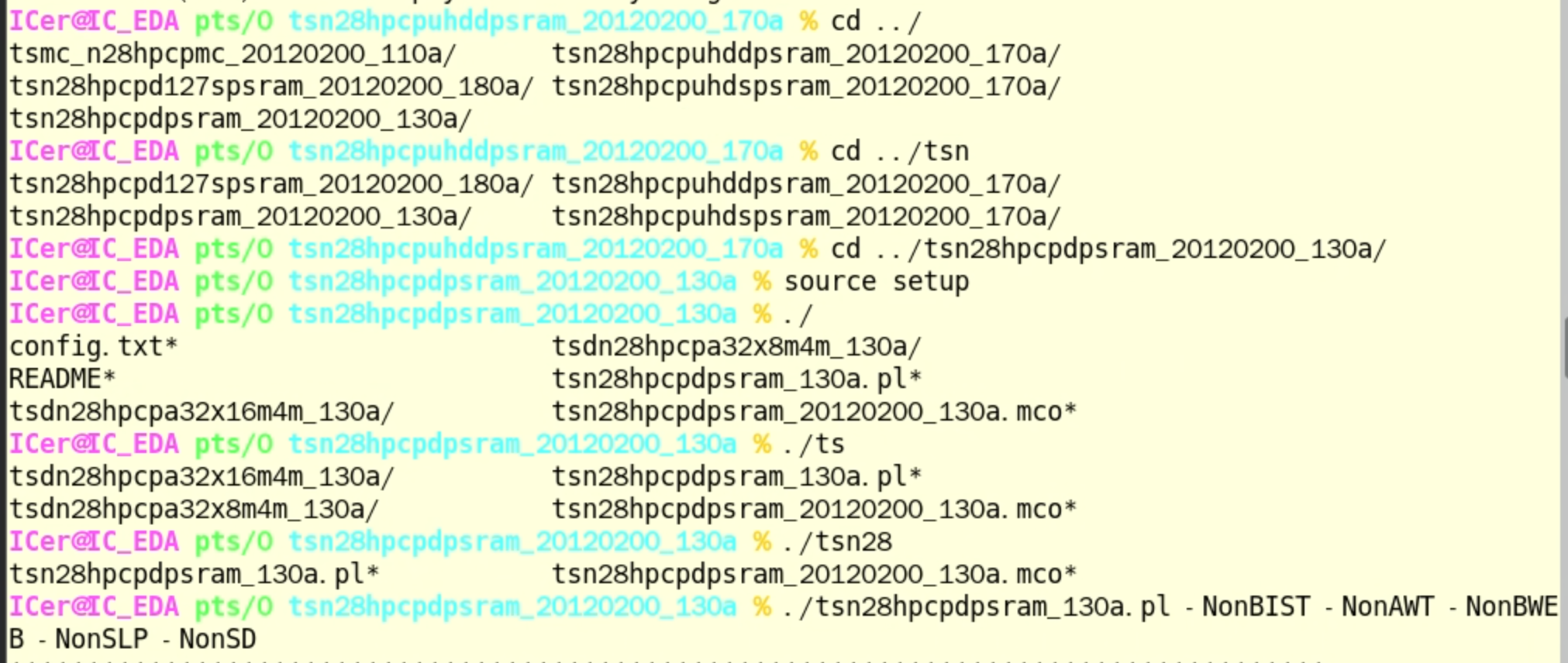

pdf中最下面的测试是使用的uhddpsram,

然后如果想使用其他的sram要cd到其他sram路径。示例看我下面的终端图。Memory complier 虚拟机使用

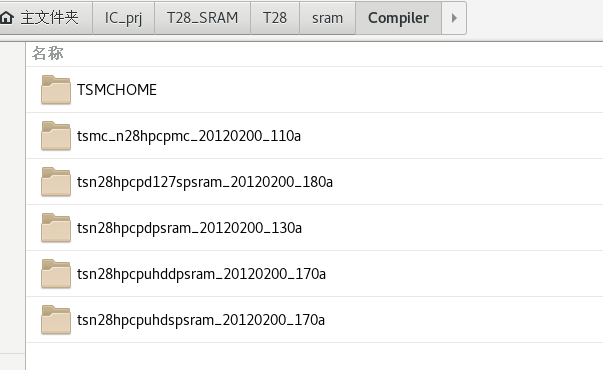

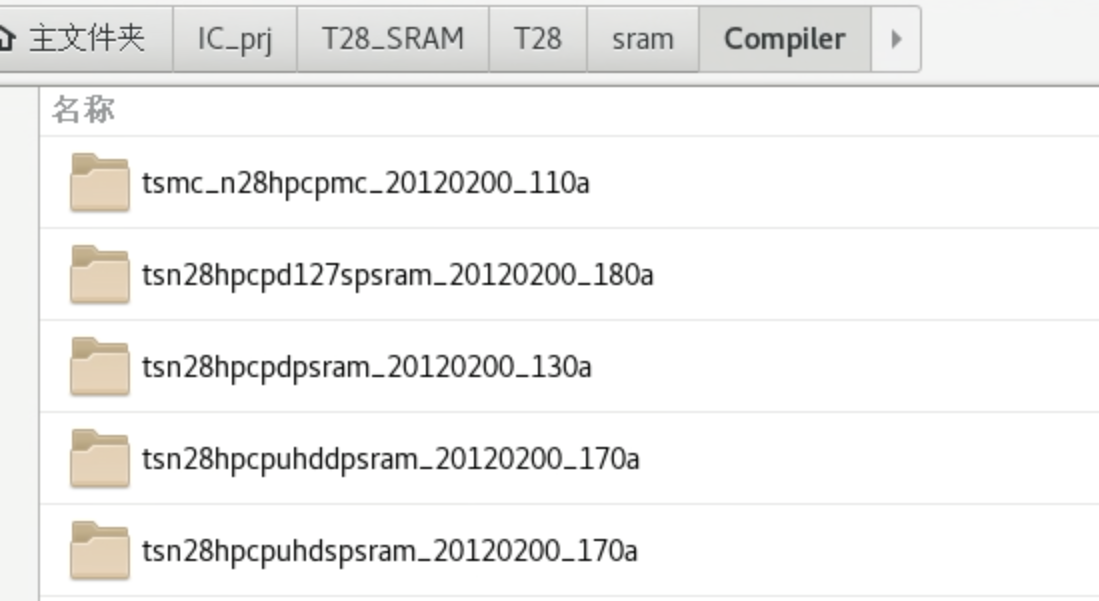

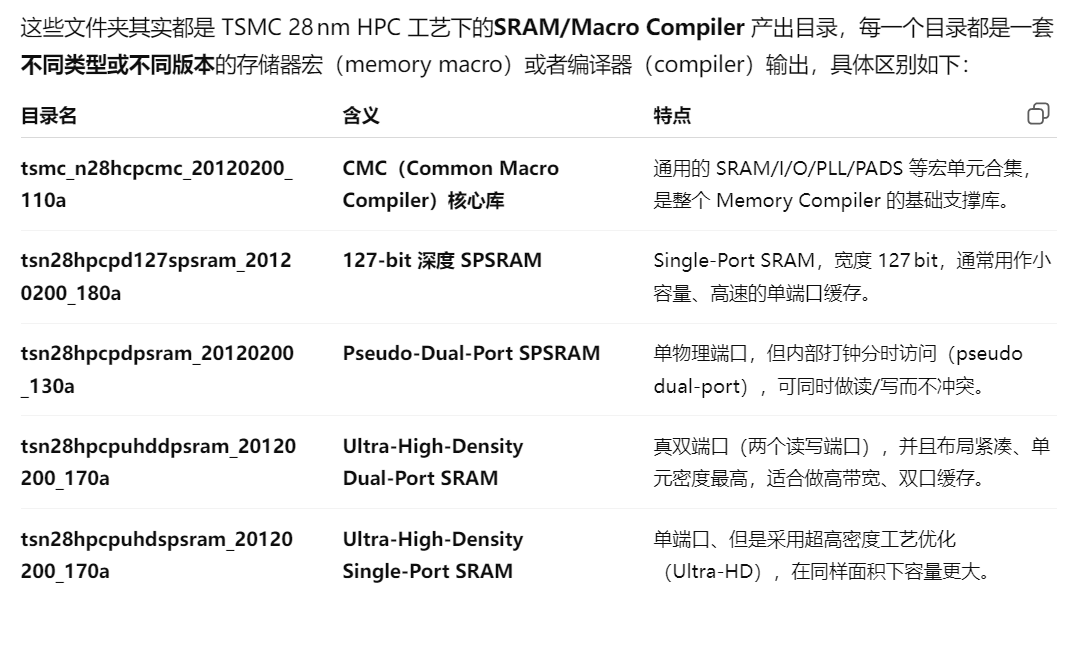

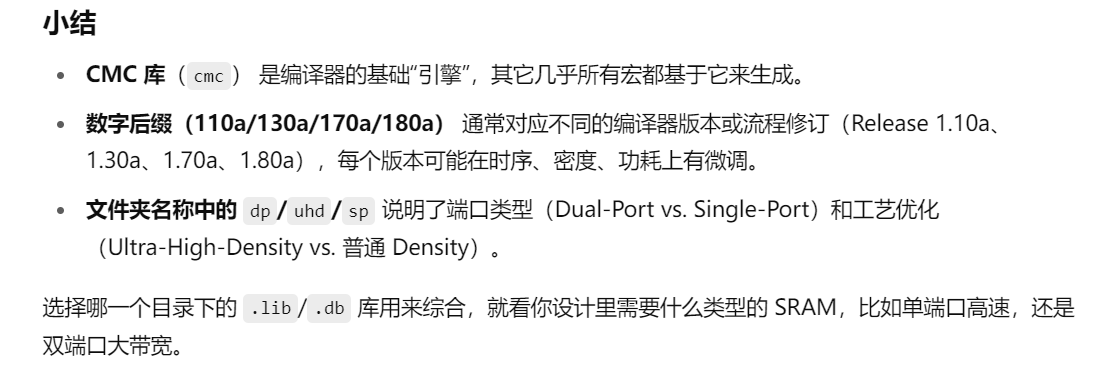

一共有4个sram类型。cd到你需要的sram类型文件夹里面。

cd到其他sram文件夹的时候也要source setup!!!!

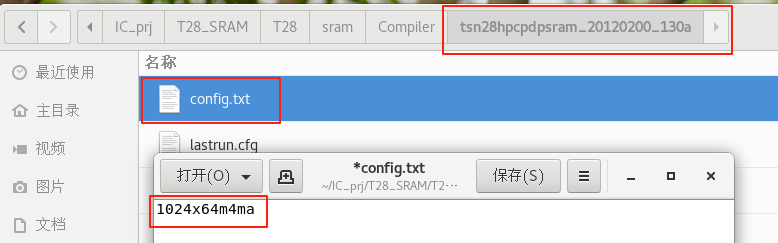

在对应的文件夹下修改config文件,填入你想获得的sram大小。最后三个字母会根据你sram的大小而不一样,命名规范看setupnote。

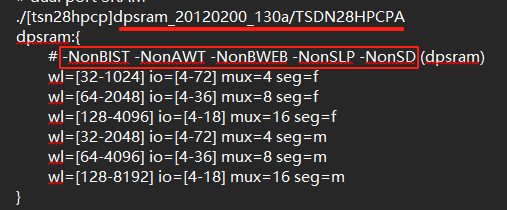

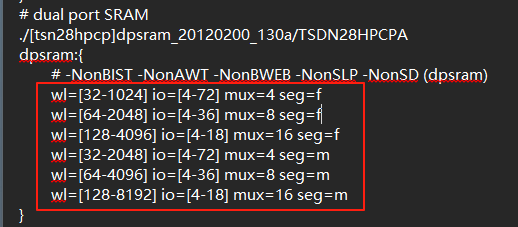

然后再执行pl文件的时候,不能直接运行,后面要跟一些参数,具体参数看setupnote,#号后面的就是具体参数,不带括号里的内容。不同型号sram参数不一样。

示例:hpcpdpsram的是这行,#号后面就是要带的命令,命令的目的就是注释一些不用的端口。

[setup_note.txt]

然后在执行了license的终端中执行对应的pl文件,带上后面的命令。

执行结束就可以在文件夹中看到生成的sram,小技巧就是看修改时间,修改时间最近的那个就是刚生成的。

hpcp后面的是sram的名称,最后的130a是版本号。

如dpsram就是双端口sram。

uhddpsram

License 关掉终端后就没有了,每次开机且每开一个终端都要重新运行license的命令。

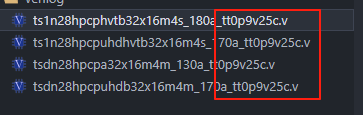

然后要把sram封装一下,先把生成的.v文件弄出来,一般都是选择这个后缀,0.9v,25度。有特殊需求可以选其他的电压温度。

参考下面的template,给他写一个top,然后再写一个tb文件测试一下能否正常读写。

top名,和模块名最好直接把sram的大小和类型写上去,更直观,如果有多个sram就不会混。

其中N,M要根据sram里面的值修改。

[_template.zip]

这个延迟好像就是为了防止verilog模型报错,综合的时候会自动忽略。